# Industrial Policy, Location Choice, and Firm Performance in High-Tech Manufacturing

#### Ran Zhuo

Ross School of Business, University of Michigan, Ann Arbor, MI 48105, ranzhuo@umich.edu

#### Audrey Tiew

Department of Economics, New York University, New York, NY 10012, audreytiew@nyu.edu

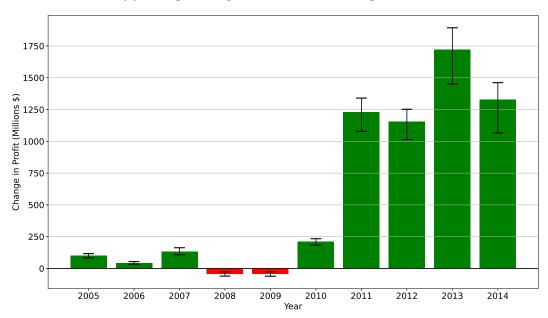

High-tech manufacturing industries face constant technological change and sustained investment pressures as manufacturing technologies evolve. National policies from the U.S. and China—driven by concerns over security and industrial self-reliance—now heavily influence these investment pressures. This paper examines the effects of industrial policy on contract manufacturing investments in the global semiconductor industry. We assemble a novel dataset that combines quarterly facility-level capacity investments with global contract manufacturing orders from 2004 to 2015. Using these data, we estimate a structural model of contracting between semiconductor manufacturers and their clients, recovering key competitive parameters. We apply the model to a detailed case study of a major semiconductor manufacturer evaluating whether to locate a large fabrication facility in the U.S. or remain in its home region amid shifting industrial policies. In counterfactual simulations, we find that locating in the U.S. would require an additional investment of \$1.2 billion compared to the home region, which could roughly be offset by lump-sum subsidies comparable (percentage-wise) to those provided under the CHIPS and Science Act. However, the profit reduction caused by cost disadvantages and reduced competitiveness at the U.S. location has a greater impact. Across various policy scenarios motivated by real-world industrial policies—including a no-policy baseline, U.S. export controls alone, Chinese tax subsidies alone, or a combination of both—locating in the U.S. consistently results in an additional \$1.6-\$1.8 billion profit loss compared to staying in the home region. This loss is concentrated in later years as the facility's technology matures. Across all simulated scenarios, industrial policies reduce manufacturing profits by \$3.1 - \$10.6 billion relative to the no-policy baseline, but U.S. import tariffs substantially change the pattern of these losses: under our conservative tariff rate calibration, relocating to the U.S. increases the firm's profit by \$5.9 billion relative to remaining in its home region, primarily by offsetting the cost disadvantages of a U.S. facility and enhancing the firm's competitiveness in capturing U.S. demand, particularly for mature technologies.

# 1. Introduction

High-tech manufacturing in industries such as biotechnology, electric vehicles, and semiconductors is characterized by rapid technological turnover, substantial fixed-cost investments, and significant economies of scale. Consider semiconductor manufacturing: building and equipping a leading-edge facility cost less than \$1 billion before the 2000s, around \$5 billion in the 2010s, and over \$10 billion in the 2020s (Taiwan Semiconductor Manufacturing Company 2020). The fundamental economics of

these industries increasingly clash with recent national policies in the U.S. and China, which emphasize domestic self-reliance in key high-tech sectors. These policies aim to boost domestic production through generous manufacturing subsidies, tax incentives, export controls, and potentially tariffs (see, e.g., The State Council of the People's Republic of China 2015, U.S. Senate Committee on Commerce, Science, and Transportation 2022a, York and Durante 2025), thereby distorting manufacturers' incentives for capacity investment across regions. While industry experts generally welcome subsidies, they caution that broad restrictions intended to decouple the global supply chains of these highly internationalized industries could undermine their long-term health and growth (see, e.g., Semiconductor Industry Association 2022, 2021).

In this paper, we examine how industrial policies in the U.S. and China may influence semiconductor manufacturers' regional capacity investment decisions. Using realistic policy bundles from both countries, we ask: If a particular set of policies had been in place during our data period, how should a manufacturer assess facility location choices to maximize long-run profit? While numerous reports from government agencies, industry groups, think tanks, and market intelligence firms have analyzed the implications of recent U.S. and Chinese policies for the semiconductor supply chain—and offered recommendations to both national governments and firms—there remains a surprising lack of data-driven, evidence-based academic research on this topic.

Most policy-oriented reports are highly qualitative, offering conclusions and recommendations based on limited macroeconomic or sector-level data (e.g., Friedberg and Boustany Jr 2020, Semiconductor Industry Association 2021, Bateman 2022, U.S. Government Accountability Office 2022, to name a few). The most data-driven analyses include Kim and VerWey (2019), which examines the potential impact of China achieving chip self-reliance; Varas and Varadarajan (2020) and U.S. Chamber of Commerce (2021), which study the effects of trade policies such as export controls and tariffs; and Varas et al. (2020), which analyzes the impact of manufacturing subsidies. In particular, Varas et al. (2020) projects that a \$50 billion U.S. manufacturing subsidy could lead to the construction of 19 new fabrication facilities and capture an additional 24% of the global manufacturing capacity needed between 2020 and 2030.

Among the few academic studies, Jacobs et al. (2022) examine the stock market impact of the 2018 U.S. ban prohibiting American firms from supplying to ZTE, a major Chinese telecommunications company. Funke and Wende (2022) theoretically evaluate the macroeconomic effects of U.S. semi-conductor export restrictions, while Park and Liu (2023) empirically investigates similar issues using multi-regional input-output data. Han et al. (2024) construct measures of technological decoupling and interdependence between the U.S. and China using patent data, and study the effects of U.S. export restrictions on the performance and innovation of Chinese firms in sanctioned supply chains.

Although the above reports and studies provide valuable insights, they typically focus on individual policies or narrow sets of interventions. Few, if any, consider how combinations of policies interact to shift market equilibrium in this highly globalized and intensely competitive industry. To analyze the effects of multiple industrial policies and their interactions and to understand firm decision-making in this complex setting, a model-based approach that explicitly captures competitive equilibrium is

essential. Two recent studies move in this direction. Goldberg et al. (2024) documents recent industrial policies in the global semiconductor sector and employs a model-based approach to detect unmeasured subsidies and to quantify how such subsidies can lower production costs through learning-by-doing. Miao (2024) develops and estimates a dynamic oligopoly model in which firms decide whether to innovate and adopt more advanced manufacturing technologies, explicitly incorporating trade disruption risk and industrial policy. To maintain tractability, the model abstracts from dynamic capacity investment, treating capacity as frictionlessly re-optimizable over time.

To the best of our knowledge, we are among the first to empirically examine how industrial policies aimed at promoting domestic self-reliance affect the capacity investment decisions of semiconductor manufacturers. We address this important research gap by combining detailed industry data with a rigorous structural model of market competition among manufacturers. Although fragmented, the data landscape in the semiconductor industry is rich and highly granular. Academic research has drawn on this detail to study a wide range of topics—including productivity (e.g., Irwin and Klenow 1994, Salomon and Martin 2008), resource allocation (e.g., Chang and Matsumoto 2022), competition (e.g., Henderson 1993, Fuchs and Kirchain 2010), innovation (e.g., Hall and Ziedonis 2001, Eizenberg 2014), vertical relationships (e.g., Terwiesch et al. 2005, Kapoor 2013, Fontana and Greenstein 2021), and market power (e.g., Gugler and Siebert 2007)—across the various product markets within the semiconductor supply chain. From a methodological perspective, several studies have estimated structural models to analyze industry dynamics in the semiconductor and electronics sectors, focusing on competition and investment decisions (Goettler and Gordon 2011, Gardete 2016, Igami 2017, 2018, Igami and Uetake 2020, Thurk 2022, Igami et al. 2024). The markets examined in these papers share key features with our focal market, including oligopolistic competition among a few large firms, a unified global market, vertical product differentiation, and sustained, capital-intensive capacity investment driven by technological progress.

Our empirical setting focuses on the contract manufacturing market in the semiconductor industry. Contract manufacturers produce chips on behalf of other companies, primarily fabless designers that lack their own fabrication facilities. Contract manufacturers play a vital role in the global semiconductor supply chain, producing chips from microprocessors for laptops to system-on-chips for smartphones and AI accelerators for large language models. Their clients include leading chip designers like Apple and Nvidia as well as customers requiring legacy chips for defense and medical applications. The market is highly concentrated: in 2017, contract manufacturing generated over \$62 billion in revenue, with Taiwan Semiconductor Manufacturing Company (TSMC) alone accounting for more than half of the top eight manufacturers' revenue. Other major players include United Microelectronics Corporation (UMC) in Taiwan, Semiconductor Manufacturing International Corporation (SMIC) in China, GlobalFoundries in the U.S., and Samsung in South Korea.

Contract semiconductor manufacturing has become a central focus of recent industrial policies in both the U.S. and China, which prioritize domestic capacity expansion through substantial direct subsidies. The U.S. CHIPS and Science Act of 2022, for example, allocates \$39 billion to support

<sup>&</sup>lt;sup>1</sup> Bollinger et al. (2024) studies a related question in the context of solar panels.

the construction and modernization of domestic fabs, alongside a 25% investment tax credit. TSMC alone has been awarded \$6.6 billion in subsidies for its \$65 billion investment in the multi-phase TSMC Arizona facility, which targets cutting-edge manufacturing. Meanwhile, China has supported its semiconductor industry since 2014 through the "Big Fund," which has invested around \$50 billion, primarily in manufacturing capacity. Other policy tools employed or proposed by both countries in recent years include export controls that restrict manufacturers from contracting with Chinese buyers, as well as tax breaks and tariffs. The rapid pace and complexity of these policy changes make it difficult to isolate the effects of individual interventions using reduced-form methods like event studies. This further motivates the use of a structural, model-based approach that explicitly captures market equilibrium to analyze the combined effects of policies and firm strategies.

The data we analyze combines various rich data sources from the industry. It includes a comprehensive, worldwide sample of facility-level capacity investments, captured quarterly from 1995 to 2015. This sample provides details on facility characteristics, installed capacity, manufacturing technology, ongoing construction and equipment investments, and the type of investment (e.g., constructing a new facility or upgrading an existing line). Additionally, we have a representative sample of global contract semiconductor manufacturing orders, collected quarterly from 2004 to 2015. This sample includes data on order quantity, price, manufacturing facility location, and technology. We enhanced these two proprietary datasets with additional, publicly available information on industry and firm performance. This supplementary information covers annual revenue figures, revenue shares by manufacturing technology generation and geographic region, gross margins, R&D spending, and capacity utilization for top contract manufacturers.

We use these data to estimate a structural model of capacity contracting between manufacturers and their clients, recovering the key parameters that determine market equilibrium during the 2004–2015 period. Accordingly, our counterfactual analysis of facility location choices also focuses on this period. This timeframe precedes the announcement or implementation of most recent industrial policies, so the industry was more likely to be in a stable equilibrium to enable reliable inference. Although national semiconductor policies have changed frequently, the shifts prior to 2015 were relatively minor compared to the significant policy changes in China and the U.S. beginning in late 2014. Moreover, the fundamental economics of the industry have not changed significantly from this period to the present. We thus believe that analyzing and exploring counterfactual scenarios from this recent historical period not only remains interesting and important but also offers useful insights for policymakers and firms today.

Our model endogenizes manufacturer profits and how they vary with the number of competitors and capacity constraints in the contract semiconductor manufacturing industry through a stylized bargaining framework. In this framework, buyers solicit bids from multiple manufacturers with available capacity for a given technology generation and period. Buyers have inelastic demand for chip quantities, reflecting downstream rigidity, and choose manufacturers to maximize their utility based on willingness to pay, possible regional preferences or subsidies, and the price charged.

Manufacturers' price bids depend on both the competitive environment and their marginal costs. When only one manufacturer bids, it sets a take-it-or-leave-it price equal to the buyer's maximum willingness to pay adjusted for regional manufacturing utility. When multiple manufacturers bid, negotiation follows an English auction where the winner prices just above the second-best competitor's marginal cost, adjusted for the buyer's regional preferences. Each manufacturer's marginal costs include common technology costs, manufacturer-specific cost advantages, capacity scale effects, regional cost differences, and private idiosyncratic shocks. Total profits aggregate over all won contracts, accounting for price, costs, and fixed overhead. This framework effectively links competition, capacity constraints, and regional factors to pricing and profitability in contract semiconductor manufacturing.

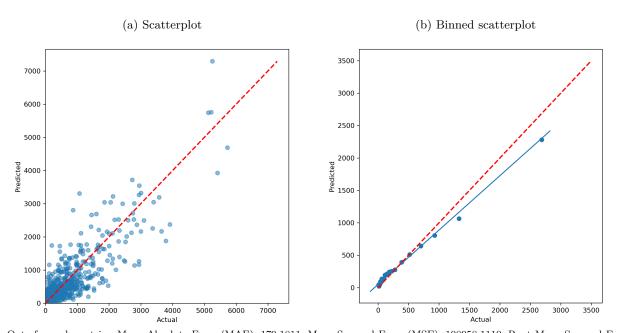

The key competitive parameters recovered from estimation include buyers' regional preferences, manufacturer-specific marginal costs, regional differences in marginal costs, and cost advantages from geographic proximity between manufacturers and buyers. These parameters are estimated using the method of simulated moments. In each iteration, simulated buyer-manufacturer negotiations generate model-implied moments, which are compared to observed moments such as gross margins, price distributions, revenue, utilization, and regional revenue shares. The estimation minimizes a weighted distance between simulated and observed moments (rescaled to make metrics like revenue and utilization comparable) using weights that balance the contribution of moment groups with differing numbers of observations. This approach enables robust identification of structural parameters that align with observed variation in prices, quantities, and firm-level outcomes across time, technologies, and regions.

The estimation results confirm key economic intuitions and provide credible quantitative insights into the global contract semiconductor manufacturing market from 2004 to 2015. The estimated parameters show that producing more advanced technologies is more costly, while costs decline over time as technologies mature. Firm- and region-specific cost differences indicate that major players like TSMC enjoy substantial cost advantages—both from firm-level efficiency (with a marginal cost that is, on average, 13.96% lower than that of the average manufacturer in Taiwan) and from regional cost savings (with a marginal cost 9.43% lower than if the same fab were located in North America). The model also identifies a significant cost benefit—on average equivalent to 7.96% of marginal cost—when buyers contract with manufacturers in the same region, underscoring the role of geographic proximity in shaping market outcomes. On the demand side, the estimates show that North American buyers dominated the market for cutting-edge technologies. However, their share has steadily declined over time and is much smaller for mature technology generations, as mainland Chinese buyers have become increasingly prominent.

We then apply the model and the estimates to a detailed case study of TSMC evaluating whether to locate a large fabrication facility in the U.S. or remain in its home region amid shifting industrial policies. While ideally we would analyze TSMC's 2020 decision to build fabs in Arizona, the Arizona facilities were developed amid frequent policy changes, so the market likely operated outside a stable equilibrium needed to enable reliable inference of key cost and competitive parameters in the baseline. To overcome these challenges, we identify comparable projects within our sample period of 2004–2015. In particular, TSMC Fab 14 in Taiwan closely matches Arizona's investment profile in many

ways, including development timeline, phased strategy, and adoption of cutting-edge technology with preplanned upgrades. The main difference is that the Arizona fab is located outside TSMC's home region and benefits from substantial government subsidies. This makes Fab 14 our ideal sandbox for simulating counterfactual scenarios, comparing maintaining Fab 14 in Taiwan versus relocating Fab 14 to the U.S., and studying how industrial policy bundles—such as subsidies, tax credits, export controls, and tariffs—affect the optimality of location decisions and competitive outcomes. These results provide insight into how policies might influence investments like TSMC Arizona.

Our counterfactual analyses of TSMC Fab 14's location choices yield several insights. First, based on facility characteristics (such as capacity, location, and technology) and the construction and equipment costs of similar projects in our facility investment data, we find that locating in the U.S. would require an additional \$1.2 billion investment compared to the home region. These additional costs could be roughly offset if lump-sum subsidies—comparable in percentage terms to those provided under the CHIPS and Science Act—were available.

However, the reduction in profit caused by cost disadvantages and reduced competitiveness at the U.S. location has a more significant impact. Across various policy scenarios inspired by real-world industrial policies—including a no-policy baseline, U.S. export controls alone, Chinese tax subsidies alone, and a combination of both—locating in the U.S. consistently results in a profit loss of \$1.6-\$1.8 billion compared to remaining in the home region. This loss is concentrated in later years, as the facility's technology matures. In the early years, competition is less intense, with fewer manufacturers capable of producing frontier technologies; proximity to high-end U.S. customers helps offset the higher production costs. Over time, as low-end demand shifts to Asia and global competition intensifies—since more manufacturers can produce at mature technology nodes—U.S.-based production becomes increasingly uncompetitive. Across these realistic policy scenarios, we find that locating in the U.S. is not a profitable strategy.

Tariffs, however, substantially alter these patterns. When Fab 14 remains at home, tariffs have a muted effect on firm profits. Given limited U.S. capacity during the sample period and inelastic buyer demand, U.S. buyers have little choice but to contract with foreign-based fabs and absorb the additional tariff-related costs. In contrast, when Fab 14 is located in the U.S., tariffs help offset the cost disadvantages of the U.S. facility and enhance the firm's ability to competitively capture U.S. demand, particularly at the low end—demand it previously had to compete for globally against low-cost overseas manufacturers. Under our conservative tariff rate calibration, relocating to the U.S. increases the firm's profit by \$5.9 billion compared to remaining in its home region. In this context, tariffs effectively counterbalance the competitive disadvantages typically faced by fabs producing mature technologies in high-cost locations like the U.S., resulting in the opposite pattern as compared to that observed under other policy combinations.

Our findings highlight the critical role of technology maturity, the differing competitive environments and market structures between advanced and mature technologies, and evolving buyer demographics in shaping high-tech manufacturing investment decisions amid intensifying geopolitical pressures. While the short-term impact on profitability may be limited when technology is at the cutting

edge, industrial policies are poised to exert a much stronger influence over the long term as technologies mature and market structures evolve. Moreover, across the various policy bundles we simulated and different potential facility locations, we consistently observe that industrial policies—such as export controls and tax incentives enacted by rival countries—adversely affect TSMC's profitability. Under our conservative calibration scenarios, these policies could reduce profits by approximately \$3.1 billion to \$10.6 billion. This significant impact underscores that the expanding scope and intensity of industrial policies are likely to fundamentally reshape firms' long-term profitability outlooks. Consequently, firms must critically reassess their capacity investment strategies, factoring in not only current market conditions but also the evolving geopolitical landscape and competitive environment as technology matures, to remain competitive and resilient.

We caution that while our study can assess how industrial policies affect manufacturers' profitability across different geographies, the current model cannot determine their welfare impact on U.S. semiconductor buyers, consumers, or other parties along the value chain. Buyers are likely to face significant welfare losses if policies such as tariffs raise the prices of chips from previously low-cost manufacturers, thereby reducing affordable options in an otherwise less regulated market. Substantial further research is needed to develop a holistic understanding of the broader societal impacts of industrial policies.

# 2. Empirical Setting

This section starts with an introduction to contract manufacturing of semiconductor chips, describing where contract manufacturing situates in the industry supply chain and the major players. We then describe more precisely the product being manufactured by contract manufacturers, the manufacturing process, and the distinction between different generations of manufacturing technologies. This will help us understand the fundamental economics of the industry. We then discuss the recent policy developments in China and the U.S. regarding domestic manufacturing of semiconductor chips, covering the main policy instruments considered or implemented by national governments. We wrap up the section by introducing the case study that anchors our analysis: a major semiconductor manufacturer (TSMC) evaluating whether to locate a large fabrication facility in the U.S. or remain in its home region amid shifting industrial policies.

## 2.1. Contract Manufacturing in Semiconductor Industry Value Chain

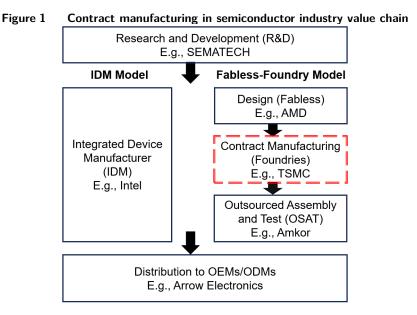

The semiconductor industry has a complex value chain with multiple models of production and a number of distinct players. Figure 1 shows a simplified illustration of where contract manufacturing situate in the industry value chain.

Chip design and manufacturing are downstream from R&D and upstream from distribution of chips to Original Equipment Manufacturers (OEM) and Original Design Manufacturers (ODM).<sup>2</sup> Abstractly,

<sup>&</sup>lt;sup>2</sup> R&D in chip design and manufacturing usually involves significant public-private partnerships, for example throught research institutes like SEMATECH. OEMs and ODMs purchase manufactured chips from chip designers. Using those chips, OEMs design and produce electronics based on the their customers' requests while ODMs design and produce electronics either to be used in their own products or to be sold under their own brand names.

Note: Adapted from Figure 3 of Semiconductor Industry Association (2016).

chip design and manufacturing can follow one of two models of production. The first model is the Integrated Device Manufacturer (IDM) model. IDMs design, manufacture, assemble, and test semiconductor chips on their own. They then sell the finished chips to the OEMs and ODMs. Before the 1980s, all semiconductor firms had intergrated design and manufacturing. The "foundry" business originates from these firms buying and selling excess capacity from other firms to even out their capacity needs (McLellan 2012).

A second model of production is the fabless-foundry model originating in the 1980s. A "fab" is short for a semiconductor fabrication plant. Fabless firms design chips and outsource chip manufacturing. As the capital requirements to build manufacturing capacities have increased significantly with newer and newer generations of manufacturing technologies, going fabless has helped many small innovative chip designers to enter the downstream market for chips. However, for fabless firms, securing spare capacity at IDMs was uncertain and risky. In response to the fabless firms' need to address capacity uncertainty, "pure-play" contract manufacturers (or foundries) came into existence with the founding of the Taiwan Semiconductor Manufacturing Company (TSMC) in 1987. When a fabless firm orders chips from a contract manufacturer, the contract specifies the quantity, technical specifications, price, delivery timeframe, and so on. Pure-play foundries do not have their own chip design businesses and exclusively manufacture chips. Outsourced semiconductor assembly and test (OSAT) firms provide third-party packaging and test services for the chips manufactured by the contract manufacturer. The finished chips are then sold to the OEMs and ODMs by the firm who designed the chips.

The distinctions we have described between different links in the value chain are not strict, and a semiconductor firm can occupy more than one position in the value chain. Notably, an IDM faced with capacity constraints can place manufacturing orders to foundries, and an IDM faced with excess capacity can take outside orders and perform contract manufacturing. An IDM, for example Samsung, may even have dedicated capacity for contract manufacturing. One main difference in manufacturing between

an IDM and a foundry is that IDM fabs are typically optimized for a limited range of products that the IDM sells downstream, whereas foundries handle a diverse product mix. For example, an Intel fab typically produces only Intel microprocessors, while a TSMC fab could manufacture microprocessors, system-on-chips used in smartphones, and AI chips.

Our analysis of contract manufacturing revenue of top contract manufacturers shows that two patterns stand out. First, pure-play foundries dominate the contract manufacturing market. Throughout 2005–2017 where we have data on contract manufacturing revenue for both top pure-play foundries and IDMs, IDMs have only accounted for 2–11% of the revenue of the top eight players in this market. Second, the market is oligopolistic and is dominated by a few big players. One firm, TSMC, accounts for 52–61% of the revenue among the top eight contract manufacturers over the period 2005–2017. Among the other leading firms, UMC and SMIC consistently rank in the top eight, accounting for 9–21% and 5–8% of the top-eight revenue during this period, respectively. The remaining positions fluctuate due to entry, mergers, and other industry dynamics.<sup>3</sup> TSMC has been by far the largest and the most important player in this market. As such, statistics on TSMC and actions taken by TSMC are often reflective and representative of the overall market conditions in contract semiconductor manufacturing.

# 2.2. The Product and Manufacturing Technology

A unit of product being manufactured is a silicon wafer with layers of integrated circuits fabricated at its surface. Each wafer carries many chips that will later be cut and packaged appropriately. See Figure 2a for an example of a wafer and Figure 2b for the circuits patterns fabricated on the wafer under a microscope. The most prevalent manufacturing process is the complementary metal-oxide semiconductor (CMOS) process, which uses light and a series of complex physiochemical reactions to transfer intricate circuit designs onto the wafer layer by layer. Our study will only focus on manufacturing capacity for the CMOS process, which accounts for 92% of the orders in our representative demand data.<sup>4</sup>

The evolution of manufacturing technology follows a numerical nanometer scale. For example, different generations are referred to as 90nm, 65nm, 40nm, and so on. Smaller technology nodes represent more advanced manufacturing capabilities than larger ones. Until the generation 28nm which entered commercial production around 2012, these numbers carry exact meaning and measures a specific physical dimension of the chip. A smaller technology node produces smaller integrated circuits fitted more tightly into the same surface area on the wafer, and delivers higher performance, more energy efficiency, and more cost efficiency for the chips. After 28nm, though shrinking the integrated circuits becomes increasingly challenging, manufacturers continue to find new ways to improve the manufacturing process to deliver more powerful chips (Semiconductor Engineering n.d.). Node names of newer generations still follow a numeric convention, but those numbers have lost their connection to the physical features on the chip. The best way to understand the meaning of a new node in recent

<sup>&</sup>lt;sup>3</sup> GlobalFoundries, formed in 2009 from the divestiture of AMD's manufacturing operations, accounts for 7–14% of top-eight revenue between 2009 and 2017. Samsung officially launched its dedicated foundry business in 2005 and accounts for 5–11% of top-eight revenue between 2010 and 2017.

<sup>&</sup>lt;sup>4</sup> The next most prevalent process, the BiCMOS process, accounts for less than 4% of the orders in our demand data.

Figure 2 Semiconductor wafer as the product

(a) Former Intel CEO Pat Gelsinger holding a wafer

Photo credit: Figure 2a from Shankland (2022) and Figure 2b from NISENet (2014).

years has become to think of it as an umbrella term, which manufacturers use in the hope that the number can help to capture the set of new manufacturing technologies capable of delivering substantive improvements in performance of the chips as compared to the previous generation (Hruska 2021). Since around 2017, which falls outside of our sample period, node names have become even more inconsistent that technical specifications of chips manufactured using the new node with the same number start to not match from one manufacturer to the next. As of now, node names are more often considered a marketing term.

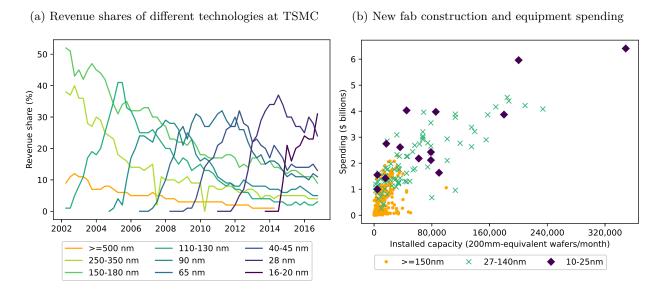

Semiconductor manufacturing is a prime example of high-tech industries characterized by substantial fixed costs and rapid technology turnover. Building a fab costs billions, and every two years, new manufacturing technology generations gain revenue share at the expense of older ones, as seen in Figure 3a. This equilibrium outcome results from both demand and supply factors. High-value chips like microprocessors require the most advanced technology, and when a leading manufacturer like TSMC introduces a new generation of technology, few competitors initially offer the same. Over time, more rivals climb the quality ladder and enter the market, leading to price competition and driving down profits. As manufacturing technologies constantly advance and become increasingly expensive, manufacturers build fewer, larger fabs for the latest tech to maximize scale economies, as shown in Figure 3b. Consequently, it is crucial for the sustained well-being of manufacturers to gain access to the widest possible market worldwide for each fab of newer generations.

## 2.3. Policy Background

Recent policies in the U.S. and China on the semiconductor industry distinguish themselves from national policies on the industry in the past by their much larger scale in direct subsidies and by their explicit focus on domestic manufacturing. While government support in the semiconductor industry has a long history and is widespread, the majority of budgetary support for the industry from national governments has historically been focused on R&D activities and tax concessions, which can be found in China, Europe, Israel, South Korea, Taiwan, and the U.S. just to name a few (OECD 2019).

Figure 3 Technology turnover and scale economies of semiconductor manufacturing

Notes: Data source for Figure 3a is TSMC quarterly reports. Figure 3b covers new fab construction worldwide between 1995 and 2015. To calculate the installed capacity, wafers of different sizes have been converted to their equivalents in wafers of 200mm in diameter, a standard practice in the semiconductor industry for capacity calculation. Spending figures are inflation-adjusted, with a base value of 100 assigned to January 2015.

The CHIPS and Science Act of 2022 is a landmark legislation in the U.S. representative of the recent policy development in the U.S. regarding the seminductor industry. The Act provides \$52.7 billion to cover an umbrella set of incentives and support around R&D, workforce development and private-public partnerships of the industry, but the centerpiece of the legislation is the CHIPS for America Fund, which includes \$39 billion in financial assistance over five years to build, expand, and modernize domestic semiconductor manufacturing (U.S. Senate Committee on Commerce, Science, and Transportation 2022a). In addition to the CHIPS Fund, the Act also created a 25% investment tax credit (ITC) for investments in semiconductor manufacturing (U.S. Senate Committee on Commerce, Science, and Transportation 2022b). Moreover, both the CHIPS Fund and the ITC also restrict recipients from building advanced semiconductor production facilities in countries that "present a national security concern," defined as China, Iran, Russia, and North Korea, for ten years after receiving an award (Swanson 2023). The U.S. Senate Committee on Commerce, Science, and Transportation cites the fact that only 12% of chips are currently manufactured domestically, compared to 37% in the 1990s, and many foreign competitors, including China, are investing heavily to dominate the industry as the main motivations for the Act. In addition, the U.S. has imposed semiconductor export controls on China (Khan 2020, Industry and Security Bureau 2020, 2022, 2023). These include list-based restrictions that limit the sale of specific advanced manufacturing equipment and chips to Chinese entities, requiring exporters to secure licenses. Moreover, end-use and end-user controls target specific Chinese entities, notably major chip producers including SMIC. Spanning a broader set of technologies, these controls generally assume a default position of denying export licenses.

Before the passage of the CHIPS and Science Act, China indeed has significantly surpassed the U.S. in providing national-level incentives targeted at semiconductor manufacturing. While the Chinese government has long had policies to support its nascent chip industry (VerWey 2019), these efforts accelerated in 2014, when China released its the Guidelines to Promote the National Integrated Circuit Industry (IC Guidelines), which laid out ambitious targets for its domestic semiconductor industry (Xinhua News Agency 2014, Semiconductor Industry Association 2021). A year later, China published the Made in China 2025 Plan, which set aspirational goals for China to achieve 70% self-sufficiency in semiconductors by 2025 (The State Council of the People's Republic of China 2015, Semiconductor Industry Association 2021). In contrast to the U.S. which had no federal level grants, subsidies, or tax incentives specifically targeted at semiconductor manufacturing between 2000 and 2020, China has set up in September 2014 the National Integrated Circuits Industry Development Investment Fund (known as the "Big Fund") which was renewed in 2019 for a second round of state financing. The two rounds of financing is totaled at \$50 billion (Semiconductor Industry Association 2020). By mid 2021, the Big Fund has invested around \$40 billion, of which 70% has been for manufacturing (Semiconductor Industry Association 2021) and the subsidies have been limited to Chinese-owned companies building domestic manufacturing capacities (Zhao 2021, Wang 2022). In addition to the funds, the Chinese national government has announced tax incentives for manufacturers operating at advanced technology nodes. For instance, manufacturers using technology nodes of 28nm and below receive a 10-year corporate tax exemption, while those with nodes of 65nm and below get a 5-year exemption (Ministry of Finance of the People's Republic of China et al. 2020). Reports have also suggested that Chinese manufacturers can obtain loans at sub-market rates from state-owned financial institutions, although the process and funding amount are opaque (OECD 2019).

Other countries and regions, including South Korea, Singapore, Japan, Taiwan, and Europe all have provided a range of grants, subsidies, tax incentives, loans, and other support for semiconductor manufacturing (Semiconductor Industry Association 2020). But the scale of their government support are significantly dwarfed by the recent policy provisions in the U.S. and China. For example, Taiwan has provided below \$1 billion in manufacturing grants and subsidies while South Korea has provided an estimate of \$7 billion to \$10 billion in manufacturing grants and subsidies between 2000 and 2020 (Semiconductor Industry Association 2020).

While the U.S. semiconductor industry largely supported and welcomed the subsidies (Semiconductor Industry Association 2022), the restrictions on investment and sales of chips in China have been a subject of heavy lobbying from the industry, which collectively earns about one-third of its revenue from China. Chip makers expressed concerns that overly restrictive measures could disrupt supply chains and hamper their global competitiveness (Swanson 2023, Hayashi and Fitch 2023). The Semiconductor Industry Association (SIA), which represents more than 95% of the U.S. semiconductor industry by revenue and nearly two-thirds of non-U.S. chip firms, states that "the semiconductor industry is truly global, and access to global markets is critical for U.S. firms to sustain high levels of investment in R&D and capital expenditure" (Semiconductor Industry Association 2021). Our conversations with industry experts also confirm that economics of scale and volume of business from the

entire global market are crucial for the health and growth of the industry. The conflicting incentives between national governments and the industry motivates this study.

It is important to note that the policy landscape for semiconductor manufacturing has been highly uncertain and continuously evolving since the early 2020s—and is likely to remain so over the next 3–5 years. Recent developments reflect this volatility. On China's side, the third phase of the Big Fund was announced in 2024 (Reuters 2024) with \$48 billions of additional financing. In the U.S., the "big beautiful bill" proposes increasing the investment tax credit (ITC) for semiconductor investment to 35% (CNBC 2025). In addition, ongoing discussions about semiconductor tariffs, which have persisted since early 2025, are likely to continue, with proposed rates reaching 25% or higher (York and Durante 2025). This continuous flux in policy not only creates a highly uncertain environment, but also makes it infeasible to isolate the effects of individual policies using an event-study framework. This motivates our use of a structural estimation and counterfactual approach to analyze the combined impact of policy bundles and firms' strategic responses under different scenarios.

## 2.4. TSMC Fab Location Case Study

To anchor our examination of how different policy bundles influence major manufacturers' location choices and performance, we study a detailed case of a major semiconductor firm's decision between locating a large fabrication facility in its home region or in the U.S. amid shifting industrial policies.

Ideally, we would directly analyze TSMC's decision to build fabs in Arizona, initially announced in 2020 with subsequent additional investments announced in the following years, as the Arizona fab cluster represents the key strategic response by the world's leading contract manufacturer to rising geopolitical tensions and U.S. policy initiatives aimed at attracting advanced semiconductor production. However, this case falls outside our sample period of 2004 – 2015, and we lack comprehensive data on firms' investment behavior, capacity, and demand conditions during this more recent period. Additionally, the Arizona facilities were developed and brought into production amid frequent policy changes, making it difficult to reliably infer key cost and competitive parameters, as the market was likely operating outside of a stable equilibrium.

To address these challenges, we identify comparable investment projects within our sample period that feature observable market conditions and outcomes under a relatively stable policy environment. This allows us to more credibly recover the key structural parameters of interest. We find the development of TSMC Fab 14 particularly relevant, as it closely resembles the investment profile of TSMC Arizona. Table 1 compares the Arizona and Fab 14 facilities, revealing TSMC's consistent fab investment approach over time while also highlighting important similarities and differences. Both facilities followed a similar four-year timeline from construction announcement to production start and launched with TSMC's cutting-edge technologies of their respective eras (4nm for Arizona in 2024; 130nm for Fab 14 in 2004). Each project adopted a phased construction and expansion strategy and demonstrated planned/actual technology node migrations, though TSMC Arizona begins at a significantly more advanced node. Fab 14 eventually transitioned to a mature node facility, typical for TSMC fabs after multiple upgrades, while TSMC Arizona's long-term trajectory remains unclear. The most notable

distinction lies in the Arizona project's substantial government subsidies and higher total investment, reflecting the growing complexity and cost of advanced-node manufacturing.

To analyze the likely impact of different industrial policy bundles, including capacity-building subsidies, tax incentives, export controls, and tariffs, we estimate key competitive parameters for the years 2004–2015 and simulate counterfactual outcomes for TSMC, comparing scenarios in which Fab 14, originally a cutting-edge facility in Taiwan, either remains in Taiwan or is hypothetically relocated to the U.S. These counterfactuals provide insight into how such policies might influence the outcomes of investments like TSMC Arizona

#### of investments like TSMC Arizona. Comparative Development of TSMC Facilities Table 1 TSMC Arizona TSMC Fab 14 in Taiwan Timeline: Timeline: • 2000: Phase 1 construction began • 2020: First fab announced, construction began • 2022: Second fab annouced • 2002: Phase 2 construction began • 2024: First fab production began in Q4 (4nm), • 2004: Phase 1 production began in Q2 (130nm) Third fab announced • 2007: Phase 2 production began in Q2 (55nm) • 2028 (planned): Second fab production (3nm) **Technology Position:** • 2030 (planned): Third fab production (2nm) • Launched with 130nm (most advanced at time **Technology Position:** of production) • Launched with 4nm (one generation behind • Multiple technology migrations: 130nm $\rightarrow$ most advanced technology at time of production) $90\mathrm{nm} \rightarrow 80\mathrm{nm} \rightarrow 65\mathrm{nm} \rightarrow 55\mathrm{nm} \rightarrow 45\mathrm{nm} \rightarrow 40\mathrm{nm}$ • Eventually settled as mature node facility • Planned migration to 3nm and 2nm nodes (40nm b/w 2008-2015) **Development Approach:** • Three-phase expansion strategy Development Approach: • 4-year timeline from announcement to produc-• Two-phase expansion strategy tion • 4-year timeline from announcement to produc-Investment & Subsidies: tion • Total investment: \$65B across three phases **Investment:**

- Government subsidy: \$6.6B from U.S. Department of Commerce (2024)

- Total investment: \$6.6B b/w 2000-2015

- No significant government subsidies noted

# 3. Data

Our unique data combine a range of rich industry data sources, including both a representative sample of worldwide contract manufacturing orders and a comprehensive sample of worldwide fab-level capacity investment. For more details about sample and variable construction as well as additional ancillary data, please see Appendix EC.1.

#### 3.1. Demand

Information on wafer orders comes from a proprietary database of wafer purchases by chip designers from contract manufacturers, collected by the Global Semiconductor Alliance (GSA), an industry organization originally founded to support fabless semiconductor firms worldwide but has expanded its membership to the entire semiconductor ecosystem. The dataset consists of individual responses to the GSA's quarterly Wafer Fabrication & Back-End Pricing Survey, detailing the orders that chip designers purchased during 2003Q4 to 2015Q3. Prior research deem the data a representative sample of wafer orders produced by the contract manufacturing sector worldwide (Byrne et al. 2017, Thurk 2022, Goldberg et al. 2024). For each order, the data report the quantity of wafers ordered, the price paid per wafer, the location of the fab, the manufacturing technology, wafer size, and the number of layers fabricated. This information allows us to examine order characteristics by manufacturing location. Although this level of product detail is remarkable, the GSA data have important limitations (Byrne et al. 2017). We only observe the country or region in which each fab was located but have no information on the producing firm or the buyer due to anonymization. Table 2 shows summary statistics of this dataset.

Table 2 Summary statistics of wafer orders, 2003Q4–2015Q3

|                                      | Count | Mean    | Std      | Min    | Max       |

|--------------------------------------|-------|---------|----------|--------|-----------|

| Quantity (# wafers)                  | 11927 | 2704.59 | 9977.55  | 1      | 53000     |

| Quantity (# 200mm-equivalent wafers) | 11927 | 3530.20 | 14946.03 | 1.00   | 530000.00 |

| Quantity $(m^2)$                     | 11927 | 3462.05 | 16741.43 | 0.44   | 466212.34 |

| Price/wafer                          | 11927 | 1578.58 | 1302.25  | 100.00 | 10340.00  |

| Price/200mm-equivalent wafer         | 11927 | 1192.93 | 651.34   | 152.00 | 8000.00   |

| $Price/m^2$                          | 11927 | 1437.13 | 1626.96  | 212.21 | 90541.48  |

| # of layers                          | 11927 | 27.66   | 8.47     | 1      | 55        |

| Wafer size (mm)                      | 11927 | 217.10  | 46.06    | 100    | 300       |

| Technology generation                | 11927 | 10.83   | 2.01     | 6      | 17        |

| Fab location                         |       |         |          |        |           |

| China                                | 11927 | 0.05    | 0.23     | 0      | 1         |

| North America                        | 11927 | 0.06    | 0.23     | 0      | 1         |

| ROW                                  | 11927 | 0.20    | 0.40     | 0      | 1         |

| Taiwan                               | 11927 | 0.69    | 0.46     | 0      | 1         |

Note: Quantity in 200mm-equivalent wafers= #wafers×(surface area of wafer ordered/ surface area of 200mm wafer). Measuring wafer quantities in 200mm equivalents is standard practice in this industry. Quantity in  $m^2 = \#$ wafers×#of layers×surface area/wafer. Price/200mm-equivalent wafer=price/wafer÷(surface area of wafer ordered/ surface area of 200mm wafer). Price/ $m^2 = \text{price/wafer}$ ÷(#of layers×surface area/wafer). Technology nodes (in nm) are converted into integer values representing technology generations. The conversion process is detailed in Appendix EC.1.8. All monetary values are in USD and are not inflation-adjusted.

Table 3 Summary statistics of fab capacity and investment, 1995Q1-2015Q4

| Table 5 Summary statistics of lab ca          | Table 3 Summary statistics of tab capacity and investment, 1995Q1–2015Q4 |          |                      |          |           |  |

|-----------------------------------------------|--------------------------------------------------------------------------|----------|----------------------|----------|-----------|--|

|                                               | Count                                                                    | Mean     | $\operatorname{Std}$ | Min      | Max       |  |

| Fab capacity                                  |                                                                          |          |                      |          |           |  |

| Capacity (wafers/month)                       | 35293                                                                    | 23405.79 | 23540.31             | 25       | 245000    |  |

| Capacity (200mm-equiv wafers/month)           | 35293                                                                    | 21698.17 | 38232.27             | 20       | 528750    |  |

| Capacity $(m^2/\text{month})$                 | 35293                                                                    | 20627.40 | 51879.50             | 2.52     | 773459.70 |  |

| IDM fab                                       | 35293                                                                    | 0.79     | 0.41                 | 0        | 1         |  |

| Wafer size (mm)                               | 35293                                                                    | 170.69   | 54.25                | 75       | 300       |  |

| Technology generation                         | 35293                                                                    | 8.65     | 3.28                 | 3        | 19        |  |

| Fab location                                  |                                                                          |          |                      |          |           |  |

| China                                         | 35293                                                                    | 0.10     | 0.30                 | 0        | 1         |  |

| North America                                 | 35293                                                                    | 0.24     | 0.43                 | 0        | 1         |  |

| ROW                                           | 35293                                                                    | 0.56     | 0.50                 | 0        | 1         |  |

| Taiwan                                        | 35293                                                                    | 0.10     | 0.29                 | 0        | 1         |  |

| Fab investment projects                       |                                                                          |          |                      |          |           |  |

| Investment amount (millions)                  | 1185                                                                     | 395.28   | 665.24               | 1.50     | 5725      |  |

| Construction investment amount (millions)     | 1185                                                                     | 62.47    | 165.19               | 0        | 1540      |  |

| Equipment investment amount (millions)        | 1185                                                                     | 332.81   | 531.00               | 0        | 4210      |  |

| Project duration (quarters)                   | 1185                                                                     | 9.09     | 7.01                 | 1        | 58        |  |

| Construction duration (quarters)              | 1185                                                                     | 1.44     | 2.27                 | 0        | 13        |  |

| Change in tech generation                     | 1185                                                                     | 2.93     | 4.60                 | -3       | 18        |  |

| Change in capacity (wafers/month)             | 1185                                                                     | 12856.94 | 19814.20             | -15000   | 175000    |  |

| Change in capacity (200mm-equiv wafers/month) |                                                                          | 17658.98 | 36264.54             | -6750    | 393750    |  |

| Change in capacity $(m^2/\text{month})$       | 1185                                                                     | 20320.27 | 45874.66             | -1487.28 | 575980.63 |  |

| Investment type                               |                                                                          |          |                      |          |           |  |

| New construction                              | 1185                                                                     | 0.26     | 0.44                 | 0        | 1         |  |

| Tech upgrade                                  | 1185                                                                     | 0.10     | 0.30                 | 0        | 1         |  |

| Capacity expansion                            |                                                                          | 0.33     | 0.47                 | 0        | 1         |  |

| Upgrade and expansion                         | 1185                                                                     | 0.18     | 0.38                 | 0        | 1         |  |

| Maintenance                                   | 1185                                                                     | 0.13     | 0.34                 | 0        | 1         |  |

Note: Capacity in  $m^2$ /month= wafers/month×predicted avg layers/wafer× surface area/wafer. Avg layers/wafer predicted by linear regression of observed avg layers/wafer for each tech generation on the tech generation ( $R^2 = 0.984$ ). Observations with extremely old technologies >3300nm dropped due to negative predicted layers. Construction duration corresponds to the observed quarters of construction spending. Project duration equals the greater of the observed quarters of construction and equipment spending or the quarters needed for the fab to reach maximum capacity within a year after the investment ends. Negative capacity change may occur when tech is upgraded. Negative tech change may occur when capacity is expanded. For new constructions, initial capacity and technology generation are set to zero, so their changes equal the constructed facility's capacity and technology generation. 86 investment projects dropped due to missing capacity information. 24 investment projects dropped where both tech change and capacity change in 200mm equivalent were nonpositive. This happened due to various reasons, such as significant changes in product mix, fabs having multiple lines that invested in older technology than their most advanced line, etc. While we hope to investigate this further, the scarcity of these observations and the granularity of data required prevent us from doing so. Projects starting before 1995Q1 or ending after 2015Q4 are excluded due to incomplete investment data outside this range, as the raw data only records investment amounts in the quarters they occurred. The rest of notes of Table 2 apply.

## 3.2. Fab Capacity and Investment

Information on fab capacity and investment comes from a proprietary database collected by SEMI, the global industry association serving the semiconductor manufacturing supply chain. The dataset we obtained covers the universe of fabs worldwide on the quarterly basis for 1995 – 2015. For each fab-quarter, the data report the installed capacity, manufacturing technology, wafer size, any ongoing investment (either in construction or equipping the fab), the type of investment (e.g., constructing a new fab or upgrading an existing fab), and investment amount. The data also provides a rich set of fab characteristics, including the location, ownership, and whether the fab manufactured specific types of products (e.g. micropressors) or was a dedicated foundry for contract manufacturing of a wide range of products. This dataset allow us to examine the capacity and investment decisions of contract manufacturers. However, it is important to note that while our data on fab investment is detailed, it lacks a breakdown of the investment amount into manufacturers' own out-of-pocket spending (through reinvestment of revenue or financing) and subsidies and other incentives received from local and national governments. These benefits are not always transparent (OECD 2019), and our data provider has confirmed the difficulty in collecting comprehensive information about government incentives in fab investments. Table 3 shows the summary statistics of this dataset.

## 3.3. Industry and Firm Performance

We supplemented our two proprietary data sources by collecting additional information on industry and firm performance from a variety of publicly available data sources. We gathered annual contract manufacturing revenue figures for top contract manufacturers from data tables released by IC Insights, a semiconductor industry intelligence firm. This dataset spans top pure-play foundries for 2000–2004 and includes both top pure-play foundries and IDMs for 2005–2017.

Additionally, we collected quarterly firm performance metrics, including contract manufacturing revenue, gross margin, R&D spending, and capacity utilization, from quarterly reports of publicly listed contract manufacturers. One limitation of this dataset is that IDMs do not separately report their contract manufacturing revenue, so our data exclusively covers pure-play foundries. Our dataset includes information for TSMC, UMC, SMIC, and four other pure-play foundries. For leading contract manufacturers like TSMC, UMC, and SMIC, their quarterly reports provide further insights into the revenue shares of different generations of manufacturing technologies and across various geographical regions. We also gather this type of information whenever it is available.

To assess the overall macroeconomic demand for semiconductors, we utilized publicly available data from the World Semiconductor Trade Statistics (WSTS) on aggregated semiconductor sales. These figures are based on net billings between semiconductor firms and their end customers, authorized distributors, and divisions or subsidiaries that manufacture end products. WSTS, a non-profit mutual benefit corporation, serves the global semiconductor industry by collecting monthly revenue data from its members and distributing it in aggregate form back to them. This data series is extensively used by the semiconductor industry to gauge overall industry demand.

## 4. Model

We endogenize manufacturer profits and how they change with the number of competitors and capacity constraints using a stylized model of bargaining, where the buyer engages in multilateral bargaining with multiple manufacturers. This model reflects key pricing drivers in the contract semiconductor manufacturing industry, including production costs and competitive pressure from rivals (Acquired 2025). Specifically, we assume buyers solicit bids from all manufacturers with available capacity for the required technology generation, with capacity fixed within each period. This structure effectively transforms the negotiation into an English auction. Each manufacturer's marginal cost decreases as installed capacity increases. Though simple, our model effectively captures how firms achieve higher markups when fewer competitors produce the same generation of technology and when they have larger capacities.

A. Preferences and Cost Function Let i denote an individual chip designer that demands contract manufacturing capacity for the generation of manufacturing technology g in period t. Buyer i's maximum willingness to pay per unit quantity of generation g in period t is denoted as  $v_{igt}$ . When more than 1 manufacturer has available capacity and participates in bidding, the buyer maximizes the following utility function by choosing which contract manufacturer, denoted as j, to use:

$$\max_{j \in \mathcal{J}_{iat}} v_{igt} + \kappa_{igt} \cdot \mathbf{1}(geog_{igt} \in \{geog_{jgt}\}) - p_{j,igt}. \tag{1}$$

$J_{igt}$  denotes the set of contract manufacturers that have available capacity and participate in bidding for i's contract. This set may include both pure-play foundries and IDMs.  $\kappa_{igt} \geq 0$  represents the shock to the buyer's utility associated with contracting with a manufacturer in the same geographic region. It can, for example, be interpreted as a government subsidy or tax exemption that benefits the buyer. The indicator function  $\mathbf{1}(geog_{igt} \in geog_{jgt})$  is equal to 1 if manufacturer j has available capacity in the same region as i, and it implies that  $\kappa_{igt}$  only affects the buyer's payoff from contracting with a regional manufacturer. We assume that  $\kappa_{igt}$  is drawn i.i.d. across i, g, t from a distribution  $H(\cdot)$ . Thus, a given buyer contracting with different regional manufacturers receives the same  $\kappa_{igt}$ .  $p_{j,igt}$  denotes the price manufacturer j charges. A transaction occurs when the j that maximizes Equation (1) results in the equation being greater than or equal to zero.

We assume that the manufacturers have a buyer-specific marginal cost of manufacturing in generation g and period t. We parametrize this cost as:

$$c_{j,igt} = \underbrace{c_{gt} + c_j - \zeta \cdot ln(Q_{gt}^j)}_{c_{jgt}} + c_{j,igt}^{geog} - \lambda \cdot \mathbf{1}(geog_{igt} \in \{geog_{jgt}\}) + \omega_{j,igt}.$$

$c_{gt}$  is the common cost of manufacturing generation g technology in period t, shared by all manufacturers.  $c_j$  is a manufacturer-specific component of marginal cost; this term allows for particular manufacturers to have persistent cost advantages.  $Q_{gt}^j$  captures available supply of capacity at manufacturer j for generation g in period t. The  $\zeta$  term approximates how marginal costs decrease with manufacturer capacity. This term captures both the scale effect and the lower opportunity costs faced by manufacturers with larger capacity when accepting orders from current buyers. The first three terms

do not vary across buyers within the same technology generation and time period for manufacturer j. To simplify the notation, we denote these terms by the letter  $c_{jqt}$ .

$c_{j,igt}^{geog}$  is the region-specific manufacturing cost for buyer i's order. A manufacturer operating multiple facilities across regions may face different marginal costs in each region.  $\lambda$  is the regional manufacturer cost advantage, which captures marginal cost savings generated by domestic manufacturing, through subsidies, lower transportation costs in the same region, and so on.<sup>5</sup> Note that  $\lambda + \kappa_{igt}$  can be interpreted as the total tax breaks, savings on tariffs, or subsidies that are realized in a given regional buyer-seller relationship.  $\omega_{j,igt} \stackrel{\text{iid}}{\sim} F(\cdot) = c_{gt} \cdot Gumbel(-\gamma \sigma_{\omega}, \sigma_{\omega})$  is an idiosyncratic error term that captures the remaining variations in the marginal cost for manufacturer j to manufacture chips for buyer i.  $\gamma$  is the Euler-Mascheroni constant.<sup>6</sup>

**B.** Negotiation Process, Information, and Timing Given a time period t, before all negotiations begin, buyers choose the technology generation g and the quantity of chips  $q_{igt}$ . We treat  $q_{igt}$  as exogenous.<sup>7</sup>  $I_{gt} \sim D_{gt}(\cdot)$  represents the number of buyers for generation g in period t, drawn from a demand distribution  $D_{gt}(\cdot)$  that evolves over time. These buyers arrive simultaneously at t and each i seeks to contract manufacturing capacity through the negotiation process with all manufacturers with available capacity.

We specify a full information negotiation game, that is, each buyer's willingness to pay, quantity of chips ordered, and each manufacturer's available capacity and marginal cost function are common knowledge, known by all manufacturers for all buyers i and generations g in period t. Let common knowledge be represented by the letter  $s_{gt}$ . The only private information in this game is  $\omega_{j,igt}$ , which is each manufacturer's own private idiosyncratic cost specific to each buyer contract. Each manufacturer only knows their own cost and the common distribution  $F(\cdot)$  from which all idiosyncratic costs are drawn.

The term  $v_{igt} + \kappa_{igt} \cdot \mathbf{1}(geog_{igt} \in \{geog_{jgt}\})$  represents the reservation price. Manufacturers participate in bidding for the buyer's contract only if they can provide positive utility; that is, when  $v_{igt} + \kappa_{igt} \cdot \mathbf{1}(geog_{igt} \in \{geog_{jgt}\}) \geq c_{jgt} + c_{j,igt}^{geog} - \lambda \cdot \mathbf{1}(geog_{igt} \in geog_{jgt}) + \omega_{j,igt}$ . If no manufacturer can offer a positive net utility to the buyer, no transaction takes place, and the buyer exits. The negotiation process and the resulting equilibrium price of the game proceed as follows.

One Manufacturer Bidding: If there is only one manufacturer with available capacity participating, we assume that bargaining takes the form of one TIOLI offer made by the manufacturer to the buyer. The transaction takes place and the manufacturer charges:

$$p_{igt}^{(1)} = v_{igt} + \kappa_{igt} \cdot \mathbf{1}(geog_{igt} \in \{geog_{jgt}\}).$$

<sup>&</sup>lt;sup>5</sup> If the manufacturer has available capacity in the same region as the buyer, we assume that the order will be manufactured in that region. If not, we assume that the order will be manufactured in a randomly selected region where the manufacturer has capacity for generation g in period t.

<sup>&</sup>lt;sup>6</sup> We adjust by  $-\gamma\sigma_{\omega}$  so that the expected mean (i.e., inclusive value) of the distribution of  $\omega_{j,igt}$  is 0 as in Allen et al. (2019).

<sup>&</sup>lt;sup>7</sup> It is reasonable to assume that the quantity and product characteristics demanded are inelastic because the quantity and the kind of chips a chip designer needs largely depend on downstream chip demand from electronics manufacturing. According to IC Insights (2022), the semiconductor content's value share in electronic systems was only 21-26% between 2004 and 2015, which corresponds to our sample period. Another justification for this assumption is the periodic capacity shortages and gluts observed in this industry. If quantities were elastic, manufacturers could have adjusted prices to smooth out the shortages and gluts.

**Multiple Manufacturers Bidding:** If there are multiple manufacturers with available capacity participating, the buyer runs a standard English procurement auction. The winning manufacturer, which we index as j = (1), charges:

$$p_{igt}^{(1)} = c_{(2),gt} + c_{(2),igt}^{geog} - \mathbf{1}(geog_{igt} \in \{geog_{(2),gt}\})(\lambda + \kappa_{igt}) + \omega_{(2),igt} + \kappa_{igt} \cdot \mathbf{1}(geog_{igt} \in \{geog_{(1),gt}\}),$$

where j = (2) indexes the manufacturer which provides the second-highest utility for the buyer (which takes into account both marginal cost and regional match benefits  $\kappa$ ).

C. Expected Manufacturer Profit If there is only one manufacturer with available capacity bidding, that manufacturer makes the following profit from each unit ordered:

$$\pi_{j,igt}(\boldsymbol{s}_{gt}) = v_{igt} + \kappa_{igt} \cdot \mathbf{1}(geog_{igt} \in \{geog_{jgt}\}) - (c_{jgt} + c_{j,igt}^{geog} - \lambda \cdot \mathbf{1}(geog_{igt} \in \{geog_{jgt}\}) + \omega_{j,igt}).$$

If there are multiple (>1) manufacturers with available capacity bidding, the expected profit of the winner (conditional on winning) per unit quantity ordered is

$$E[\pi_{j,igt}(\boldsymbol{s}_{gt})] = E[p_{igt}^{(1)}(\boldsymbol{s}_{gt})] - (c_{(1),gt} + c_{(1),igt}^{geog} - \lambda \cdot \mathbf{1}(geog_{igt} \in \{geog_{(1),gt}\}) + \omega_{(1),igt}),$$

and each manufacturer j wins with probability

$$P_{j,igt}[winner(\boldsymbol{s}_{gt})] = \frac{exp(-(c_{jgt} + c_{j,igt}^{geog} - \mathbf{1}(geog_{igt} \in \{geog_{jgt}\})(\lambda + \kappa_{igt}))))}{\sum_{j' \in \mathcal{J}_{igt}} exp(-(c_{j'gt} + c_{j',igt}^{geog} - \mathbf{1}(geog_{igt} \in \{geog_{j'gt}\})(\lambda + \kappa_{igt}))))}$$

v does not appear in the above expression because they are common across all participating manufacturers with available capacity. If manufacturer j is the winner, then its expected price is

$$\begin{split} E[p_{igt}^{(1)}(\boldsymbol{s}_{gt})] &= \sum_{k \in \mathcal{J}_{igt} \backslash j} \left( \frac{exp(-(c_{kgt} + c_{k,igt}^{geog} - \mathbf{1}(geog_{igt} \in \{geog_{kgt}\})(\lambda + \kappa_{igt}))))}{\sum_{j' \in \mathcal{J}_{igt} \backslash j} exp(-(c_{j'gt} + c_{j',igt}^{geog} - \mathbf{1}(geog_{igt} \in \{geog_{j'gt}\})(\lambda + \kappa_{igt}))))} \right. \\ &\times E[(c_{kgt} + c_{k,igt}^{geog} - \mathbf{1}(geog_{igt} \in \{geog_{kgt}\})(\lambda + \kappa_{igt}) + \omega_{k,igt} + \mathbf{1}(geog_{igt} \in \{geog_{jgt}\})\kappa_{igt})|k = (2)] \right) \end{split}$$

The order-level expected profit for j contracting with i is the quantity  $q_{igt}$  multiplied by the expected profit upon winning,  $E[\pi_{j,igt}(s_{gt})]$ , and the probability of winning (conditional on j participating in bidding for i's contract). The total expected profit of manufacturer j in period t sums the order-level expected profits across buyers where j participates in bidding and across technology generations and subtracts other fixed cost of goods sold, such as labor costs and manufacturing overhead, which we represent by  $C_{jt}$ :

$$E[\pi_{jt}(\boldsymbol{s}_t)] = -C_{jt} + \sum_{g} \sum_{i} E[\pi_{j,igt}(\boldsymbol{s}_{gt}) \cdot P_{j,igt}[winner(\boldsymbol{s}_{gt})] \cdot q_{igt}.$$

## 5. Model Estimation

## 5.1. Parameterization, Identification, and Calibration

At any given t, as g becomes more cutting-edge, the common cost of manufacturing  $c_{gt}$  becomes larger. At any given g, as t goes on,  $c_{gt}$  becomes cheaper. Thus, we parameterize  $c_{gt}$  as a function of generation g and period t:

$$c_{at} = \alpha_0 g^{\alpha_g} t^{\alpha_t}. \tag{2}$$

The parameters pinning down  $c_{gt}$  are identified by the variation in average prices by generation and over time. In particular,  $\alpha_g$  captures how relative to some base cost  $\alpha_0$  corresponding to our earliest observed generation and time period, average costs change across generations, and  $\alpha_t$  similarly captures how average costs vary across time.<sup>8</sup>

$c_j$  is parameterized as a fraction of  $c_{gt}$ , that is,  $c_j = \tilde{c}_j \cdot c_{gt}$ . A cost-competitive manufacturer may have a negative  $\tilde{c}_j$ , while a high-cost manufacturer may have a positive  $\tilde{c}_j$ . The value of  $\tilde{c}_j$  for each j is identified through variation in the manufacturer's revenue share. We assume that smaller pure-play contract manufacturers for which we do not observe revenue (they collectively account for less than 10% of the contract manufacturing market) share the same value of  $\tilde{c}_j$ , which we normalize to zero. Additionally, we assume that IDMs share the same, relatively large positive value for  $\tilde{c}_{IDM}$ , given that their fabs are not optimized for handling the diverse product mix characteristic of contract manufacturing. The revenue share of IDMs within the total contract manufacturing market identifies  $\tilde{c}_{IDM}$ .

$c_{j,igt}^{geog}$  takes four possible values:  $c^{CN}$ ,  $c^{NA}$ ,  $c^{ROW}$ , and  $c^{TW}$ , representing the region-specific manufacturing cost for mainland China, North America, Rest of the World, and Taiwan respectively. Each of these four terms is parameterized as a fraction of  $c_{gt}$ , that is  $c^{geog} = \tilde{c}^{geog} \cdot c_{gt}$ .  $\tilde{c}^{ROW}$  is normalized to zero. These terms are identified by changes in revenue shares of manufacturers that operate facilities in multiple regions when their capacity composition across regions changes.

$\zeta$  captures the decrease in marginal cost as a manufacturer's installed capacity for a technology generation increases. This term is parameterized as a fraction of  $c_{gt}$ , that is  $\zeta = \tilde{\zeta} \cdot c_{gt}$ . Variation in utilization across manufacturers and over time, driven by changes in installed capacity, helps identify  $\zeta$ .

$\omega_{j,igt}$  captures variation in prices not explained by generation-period or firm-specific means.  $\sigma_{\omega}$  is identified by these remaining price variations.

The other fixed cost of goods sold,  $C_{jt}$ , is parameterized as follows:

$$C_{jt} = \sum_{k \in K_{jt}} C^{geog} \cdot ln(Q_{jt}^k),$$

where  $Q_{jt}^k$  is the installed capacity of facility k that manufacturer j operates.  $C^{geog}$  varies by region, with three region-specific values:  $C^{CN}$  (China),  $C^{NAROW}$  (North America and ROW), and  $C^{TW}$  (Taiwan). The  $C^{geog}$  terms are identified through occurrences of negative gross margins among manufacturers in different regions. We do not have data on margins for any manufacturer in North America, so we combine North America and ROW into one variable. The overall cost is the sum of facility-specific costs.

In principle, buyer willingness to pay  $(v_{igt})$  could be identified when only one manufacturer participates in bidding, as the equilibrium price would equal the buyer's willingness to pay plus any regional manufacturer benefit  $(\kappa_{igt})$ . However, we do not observe monopoly situations in our data where only

$<sup>^{8}</sup>$  g=5 and t=2003Q3 are normalized to a value of zero in this equation.

<sup>&</sup>lt;sup>9</sup> The only exception is Samsung, which had dedicated foundries for contract manufacturing during our sample period. We estimate its  $\tilde{c}_{samsung}$  separately from the rest of the IDMs.

a single contract manufacturer is available for specific technology generations and periods.<sup>10</sup> Additionally, since we lack visibility into which manufacturers actually negotiate with each buyer, we do not impose participation constraints based on reservation prices. Instead, we allow all manufacturers with available capacity for each technology generation and period to participate in bidding, ensuring multiple bidders in all cases. With multiple manufacturers participating,  $v_{igt}$  cancels out in the expressions for equilibrium prices, probability of winning, and profit. Therefore, this term remains unidentified, and we do not parameterize it.

We assume that  $\kappa_{igt} = c_{gt} \cdot \tilde{\kappa}_{igt}$ , where  $\tilde{\kappa}_{igt}$  is drawn from an exponential distribution  $H(\cdot) \equiv Exp(\sigma_{\kappa})$ , and  $\lambda = c_{gt} \cdot \tilde{\lambda}$ , where  $\tilde{\lambda}$  is a constant parameter.  $\tilde{\lambda}$  is identified by differences in the revenue share from Chinese buyers between mainland Chinese and Taiwanese manufacturers.  $\sigma_{\kappa}$  is separately identified by variation in this share across periods and manufacturers.

The demand distribution  $D_{gt}(\cdot)$  is parameterized as a deterministic categorical distribution  $d_{gt}(geog_i|\cdot)$  of contract share by buyer geographical location multiplied by a fixed distribution of contract share by distance to technology frontier  $d(g_t^{max} - g_{it})$ , scaled by the WSTS semiconductor end product sales time series and a demand scaling parameter  $\sigma_D$ :  $D_{gt}(\cdot) = \sigma_D \cdot WSTS_{t+1} \cdot d(g_t^{max} - g_{it}) \cdot d_{gt}(geog_i|\cdot)$ . Because we observe both price and quantity for a representative set of orders, total revenue in the contract manufacturing market helps identify the demand scaling parameter  $\sigma_D$ .

For simplicity, we assume buyer locations fall into three categories: mainland China (CN), North America (NA), and the rest of the world (ROW), since mainland China and North America are at the center of the recent policy changes. We parameterize the share of contracts from buyers in these regions,  $d_{qt}(geog_i|\cdot)$ , t as follows:

$$\begin{split} d_{gt}(geog_i = CN|g_{it}, t) &= \frac{exp(l_0^{CN} + l_1^{CN}(g_t^{max} - g_{it}) + l_2^{CN}t)}{1 + \sum_{geog}^{\{CN, NA\}} exp(l_0^{geog} + l_1^{geog}(g_t^{max} - g_{it}) + l_2^{geog}t)} \\ d_{gt}(geog_i = NA|g_{it}, t) &= \frac{exp(l_0^{NA} + l_1^{NA}(g_t^{max} - g_{it}) + l_2^{NA}t)}{1 + \sum_{geog}^{\{CN, NA\}} exp(l_0^{geog} + l_1^{geog}(g_t^{max} - g_{it}) + l_2^{geog}t)} \\ d_{gt}(geog_i = ROW|g_{it}, t) &= \frac{1}{1 + \sum_{geog}^{\{CN, NA\}} exp(l_0^{geog} + l_1^{geog}(g_t^{max} - g_{it}) + l_2^{geog}t)} \end{split}$$